ニュース

“6万量子ビットの量子コンピューター”相当で名刺サイズのアニーリングマシンを日立が開発。エネルギー効率の向上でIoT機器への実装が可能に

2019/02/20 15:01

アニーリングマシンの主な適用分野は、組み合わせ最適化問題の計算。日立によると、組み合わせ最適化問題において、従来型コンピューター(Intel Corei7-6700K、4.00GHz)の約2万倍高速で計算可能なことと、エネルギー効率が約17万倍に向上したという。

名刺サイズとしたのは、スマートフォンやカメラ、センサーなどのIoT機器でリアルタイムに行うエッジ処理への適用可能性を見据えてのもの。CMOSアニーリングマシンにより、複雑な社会課題の解決や超スマート社会の実現に貢献することを目指す。

日立は昨年、CMOSアニーリングマシンを発表し、パートナー向けに無償提供を開始した。しかし、商用サービス提供で先行する富士通の「デジタルアニーラ」よりもスペックで劣勢にあったことから、次の展開に注目が集まっていた。今回のCMOSアニーリングマシンは、IoT分野という新たな領域を切り開くものであり、量子コンピューターの実践運用の向けたきっかけになると期待される。

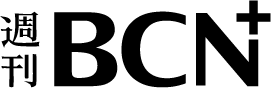

日立は今回、パラメータ(量子ビットに相当)の値を保持するメモリーセルへのデータアクセスを高速化することで、演算順序に従って一つの演算回路を四つのパラメータグループの間で切り替えながら共有できる技術を開発。四つのパラメータグループで切り替えるのは、CMOSアニーリングマシンが最適化問題の計算において、四つのグループごとに順次計算を行うため。これにより、1チップで3万976パラメータの高集積化に成功した。

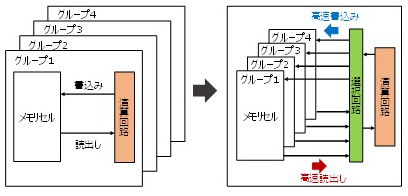

また、半導体チップの端部に、別チップのパラメータの値をコピーするための補助領域を設け、パラメータグループを計算する間に、次のパラメータグループのコピーを完了できるチップ間接続技術を開発。このチップを2枚接続し、名刺サイズで6万1952パラメータの最適化問題の計算が可能なCMOSアニーリングマシンを実現した。

日立は今後、産学連携による協創やオープンイノベーションを通じ、CMOSアニーリングマシンの普及を図るとともに、エッジ処理を見据えたコア技術の確立を目指す。

- 1

関連記事

NTTデータの量子コンピューター事業 実機で実証実験をスタート まずは20社の枠で業務応用の検証を行う

量子コンピューターの量産が可能な標準仕様となる統合システムを発表 かつての「IBM PC互換機」を彷彿――IBM

デジタルアニーラの第2世代がサービス開始、オンプレミス版も2月から提供。量子コンピューター市場の活性化に期待

東証一部上場後の新たな一歩として量子コンピューター事業に本格参入 ノウハウの早期蓄積で新たな市場での地位確立を目指す――テラスカイ